DAC 3560C Jan/2004

# DAC 3560C Audio Subsystem with Power Amplifiers and Power Management

The DAC 3560C is a single-chip, high-precision, dual digital-to-analog converter designed for audio applications. The IC employes a conversion technique based on oversampling with noise-shaping. With the implementation of Micronas' unique multibit sigma-delta approach, high linearity, less sensitivity to clock jitter, and an enhanced S/N ratio have been achieved. The DAC 3560C is controlled via SPI or I<sup>2</sup>C bus.

Digital audio input data is received via a versatile I<sup>2</sup>S interface. The IC provides three integrated power audio outputs for a stereo headphone, a mono earpiece, and a mono loudspeaker. Mixing of additional analog audio sources to the D/A-converted signal is also supported.

For applications with a noise-critical power supply environment, the DAC 3560C is equipped with a low-dropout regulator (LDO).

The IC is designed for all kinds of applications in the audio and multimedia field, such as mobile phones, PDAs, and digital audio players.

### **Features**

- Three integrated short-circuit-protected power audio outputs

- Stereo headphone output (25 mW at 2.85 V, 80 mW at 5 V)

- Mono earpiece output (100 mW at 2.85 V, 300 mW at 5 V)

- Mono loudspeaker output (400 mW at 3 V, 1.1 W at 5 V)

- Integrated LDO

- ◆ >100 dB PSRR

- DAC with 98 dB dynamic range

- Continous sample rates from 8 kHz to 192 kHz

- Analog stereo and mono line inputs with programmable gain

- Pop-free power on and off of audio outputs

- Capacitor-free headset connection

- I<sup>2</sup>C/SPI compatible serial control ports

- I<sup>2</sup>S digital audio interface

- Programmable power management

- → -30 dB to 6 dB analog volume, mute

- 2.2 V to 5.5 V supply voltage

- 1.8 V to 5.5 V digital I/O voltage

- Zero-power and stand-by mode

## **Applications**

- PDAs

- Mobile and cordless phones

- Hand-held terminals

- Portable MP3/CD/DVD players

## **Package**

40-pin Plastic Quad Flat No-leads package (PQFN40) DAC 3560C Jan/2004

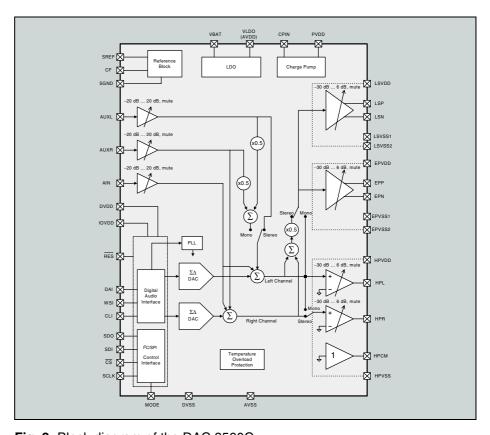

### **System Architecture**

The DAC 3560C provides three audio driver outputs capable to drive up to  $2{\times}80$  mW/ 300 mW into  $32~\Omega$  loads and up to 1.1 W into  $8{\text -}\Omega$  loads. Either digital or analog audio can be delivered to the DAC 3560C. Digital audio data is sent to a multi-bit sigma-delta DAC via an I²S-compatible interface. All internal oversampling clocks are derived from the I²S clock input by means of the internal PLL. Analog audio sources can be mixed to the digital data via one mono and two stereo line inputs. All line inputs have programmable gains.

The I<sup>2</sup>C/SPI-compatible control interface provides full control over the DAC 3560C thus allowing configuration of various sample rates, gain/volume settings of the analog inputs/outputs, as well as the possibility to power on/off signal chains in order to optimize power consumption. The audio drivers' outputs can be ramped up or down from or to their quiescent level to suppress audible pops during power-on or power-off.

For applications with a noisy power supply, the DAC 3560C contains a low-dropout regulator which can be used to improve the PSRR of the headset/earpiece driver to >100 dB at supply voltages as low as 3 V. If the PSRR is a non-critical parameter, then the DAC 3560C can be used without the LDO, allowing a lowered supply limit of 2.2 V.

Furthermore, the digital I/O-Interfaces have a separate supply pin which provides an I/O-supply voltage as low as 1.8 V thus allowing direct DSP and  $\mu C$  connection.

The DAC 3560C allows a capacitor-free headphone connection which makes the bulky coupling capacitor redundant. The IC requires only few external components leading to optimized system costs and reduced PCB area. The DAC 3560C is ideally suited for applications in ultra-flat housings.

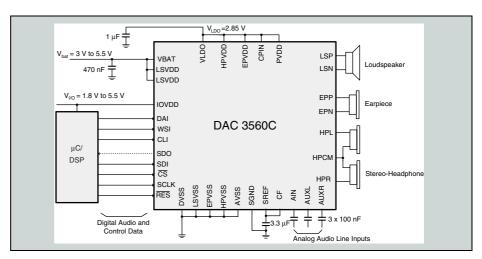

Fig. 1: Typical application circuit

Fig. 2: Block diagram of the DAC 3560C

All information and data contained in this product information are without any commitment, are not to be considered as an offer for conclusion of a contract, nor shall they be construed as to create any liability. Product or development sample availability and delivery are exclusively subject to our respective order confirmation form. By this publication, Micronas GmbH does not assume responsibility for patent infringements or other rights of third parties which may result from its use.

No part of this publication may be reproduced, photocopied, stored on a retrieval system, or transmitted without the express written consent of Micronas GmbH.

Edition Jan. 14, 2004; Order No. 6251-588-2PI